¿Cuál es el voltaje de pellizco para un JFET?

Tensión de pellizco JFET

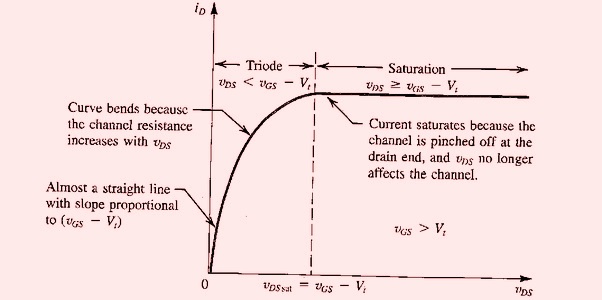

El «pellizco» no está bloqueado. Durante la operación de pellizco, la corriente de descarga no cae a cero. En cambio, la corriente Id se vuelve constante y permanece relativamente independiente del voltaje Vds. El modo de «pellizco» en los transistores FET es similar a la región operativa lineal de los transistores BJT.

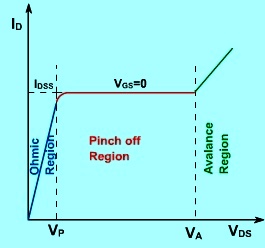

Voltaje de pinza: El voltaje de pinza es el drenaje a la fuente voltaje después del cual el drenaje a la fuente de corriente se vuelve casi constante y JFET entra en la región de saturación. y se define solo cuando el voltaje de la puerta a la fuente es cero.

Pellizca el voltaje en jfet

Con el gancho de fuente común de un canal JFET a N, dado que el voltaje de puerta Vgs se vuelve cada vez más negativo, el canal se vuelve más estrecho a medida que las zonas de agotamiento móvil invaden el canal desde el costado.

¡Finalmente, estas Áreas de Agotamiento se encuentran pero el canal no se cierra! En cambio, el canal se convierte en un largo pasaje de ancho constante. Dentro de este canal, se producen avalanchas mientras pequeñas porciones del canal intentan cerrarse. Pero cada vez que esto sucede, aparece un voltaje mayor a través de la parte cerrada, lo que hace que el DZ regrese y abre el canal nuevamente.

Durante el pinch-off el canal se comporta de forma muy extraña: ya no es una resistencia. En cambio, cuando aumenta el voltaje Vds de la fuente de drenaje, ¡el canal conductor crece físicamente por más tiempo! Es una resistencia mágica, una resistencia que intenta mantener una corriente constante incluso frente a los voltajes variables que se encuentran en ella.

¿Qué es el voltaje de pellizco?

Un FET de pellizco es una fuente de voltaje controlado de voltaje constante, mientras que un FET externo de pellizco es una resistencia de voltaje controlado. Por ejemplo, podemos usar FET como resistencias variables para actuar como controles de volumen de audio o potenciómetros analógicos. Lo hacemos manteniendo el valor Vgs bajo, para que el canal permanezca completamente abierto y no entre en modo Pinch-off.

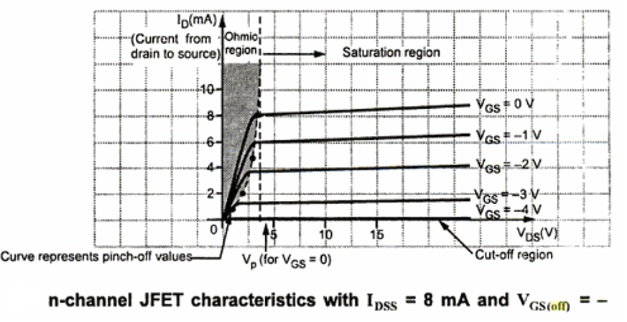

Si observamos el conjunto de curvas operativas de un FET, el gráfico Id/Vds, el modo de pellizco está en la región donde las curvas Id tienen una punta plana, o se inclinan ligeramente hacia arriba con fuertes aumentos de voltaje Vds.

Entonces, si esto es un pellizco, ¿qué es «pellizco cerrado»? Esto se encuentra en la parte inferior de la familia de curvas en valores de Vgs grandes, donde el canal está realmente cerrado y Id es cero para todos los valores de Vds.

Modo de pellizco cerrado versus modo de pellizco

Finalmente, ¿de dónde viene el malentendido entre «pellizcar cerrado» y «modo Pinchoff»? Tal vez sea porque cuando comience el Pinch-off, la resistencia de CA del canal de fuente de drenaje aumentará hasta las estrellas.

Se vuelve muy grande, idealmente infinito (lo que hace que las curvas V/I se vuelvan planas). Pero esto no es una resistencia CC. Puede haber una amplitud fluyendo hacia el circuito de escape de su mosfet de potencia, aunque la resistencia de descarga de CA sea inmensa.

Ésta es la característica principal de cualquier fuente de corriente constante. Tiene una corriente importante, mientras que para AC y cambios dinámicos se comporta como un circuito abierto.

Pero el ohmio infinito y el «circuito abierto» no significan corriente cero en lo que respecta a las fuentes de corriente. Y así, cuando Vgs se hace grande y el canal se convierte en una fuente de corriente, no se cierra. ¡Pero es todo raro! Ingrese al modo de operación de pellizco.

¿Cómo se calcula el voltaje de pellizco?

La tensión de pinzamiento Vp es el valor de Vds en el que la corriente de drenaje se vuelve constante e igual a Idss y siempre se mide con Vgs = 0 V. La desconexión se produce para valores de VDS inferiores a VP, si VGS no es igual a cero. . Aunque VP es una constante, el valor mínimo de VDS en el que ID se vuelve constante varía con VGS.

¿Para qué podemos usar el diodo además de la rectificación en un circuito?

¿Qué hace que un diodo PIN sea especialmente adecuado para un fotodetector?

¿Por qué los dispositivos electrónicos tienen frecuencias fijas establecidas en 50 Hz y 60 Hz?

¿En qué se diferencian los inversores de turbinas eólicas de los inversores fotovoltaicos?